Problem: T05-CAT/P03-UF2 set up down.

Troubleshooting route & solution:

-

Conclusion: N/A.

Remarks: N/A.

Done by: Edmar Estrada Espiritu (Wafer Sort Team, Line Engineer).

Teradyne Catalyst

Problem:

- BCM5705 fail of FAIL_VBIAS.

- Source 3 calibration failed on T07-CAT.

- T01-CAT failing DCST, UBAPUST, HCUST, HSD_ST and VHCWST.

- T05-CAT/P03-UF2 set up down.

Date: 03/16/04

Problem:

T05-CAT/P03-UF2 set up down.

Troubleshooting route & solution:

-

Conclusion:

N/A.

Remarks:

N/A.

Done by: Edmar Estrada Espiritu (Wafer Sort Team, Line Engineer).

Date: 12/17/04

Problem:

T01-CAT failing DCST, UBAPUST, HCUST, HSD_ST and VHCWST.

Troubleshooting route & solution:

- Re-run individual checker for the test failures.

- DCST - Run individual checker, passed.

- UBAPUST - Run individual checker, passed.

- HCUST - Run individual checker, failed. (See datalog)

- HSD_ST - Run individual checker, failed. (See datalog)

- VHFCWST - Run individual checker, failed. (See datalog)

- Run power_mi_st, passed.

- Check the datalog failure of the 3 tests from the datalog above.

- "There is an ALARM error - TestsALARM: Source #1 (60V UBVI) type: Overload alarm".

- Changed the 60V UBVI - Source#1 (located at UB_SPS_CAGE mainframe) eventhough the dcst checkers passed.

- Re-run all the individual tests (HCUST, HSD_ST and VHFCWST), all passed.

Conclusion:

60V UBVI - Source#1 causing the failures.

Remarks:

N/A.

Done by: Edmar Estrada Espiritu (Wafer Sort Team, Line Engineer).

Date: 11/08/04

Problem:

Source 3 calibration failed on T07-CAT.

Troubleshooting route:

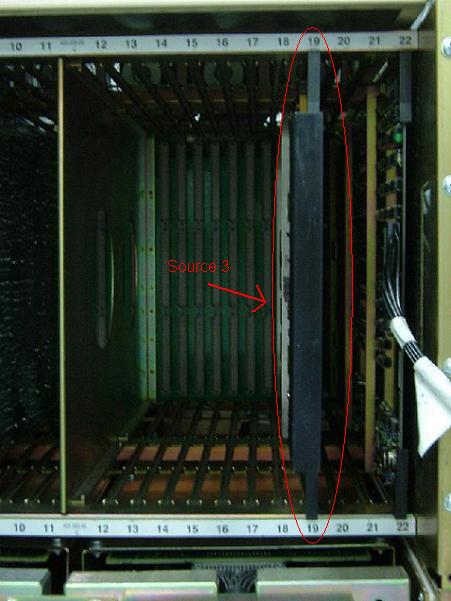

- Perform DCST checkers, Source 3 calibration failed.

- Resit Source 3 board at Backplane 2, still failed.

Source 3 board at Backplane 2

- Change board location from Slot 19 to Slot 20, still failed.

- Swap board between Backplane 2 Slot 20 & Backplane 1 Slot 14, failure still on Source 3.

Solution:

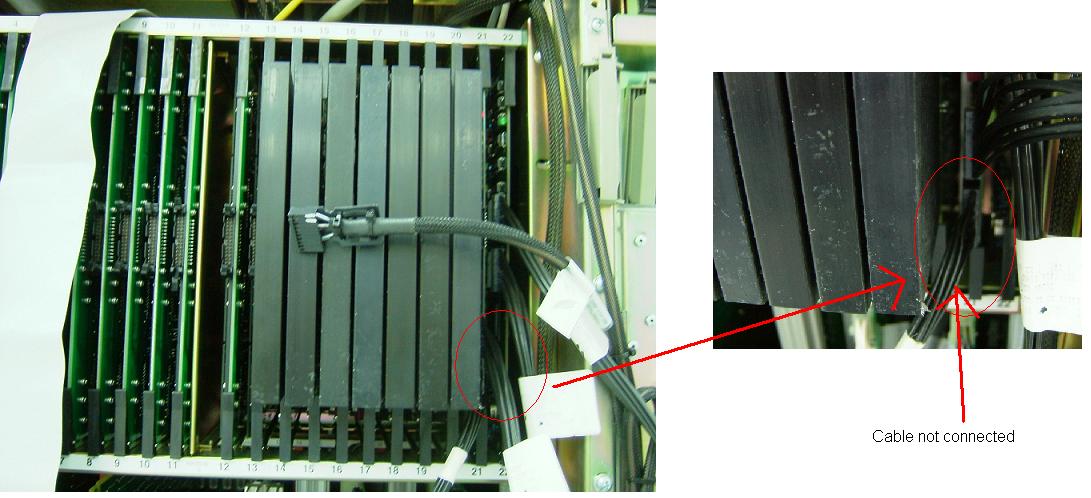

- Observe that one of the cable is not connected.

Unconnected cable

- Plug in the cable and run DCST checker, passed.

Conclusion:

No connection from Backplane 1 to Backplane 2 causing Source from Backplane 2(Source 3) failed.

Remarks:

N/A.

Done by: Edmar Estrada Espiritu (Wafer Sort Team, Line Engineer).

Date: 03/30/04

Problem:

BCM5705 fail of FAIL_VBIAS.

Troubleshooting route:

- Execute calibrate -dc -tms -hsd, still failing.

- Shutdown the tester, and reload the test program, still failing.

- Undocked and reset both loadboard and probecard (clean probecard offline), still failing.

- Run power_mi checkers found that SWPS1 Slot 5 5.2V supply was failing (this is the HSD TESTHEAD POWER)

- Adjusted the 5.2V supply, okay. Reload the test program and found that hfdig#1 calibration failing which affects

AC calibration which is also failed.

- Note: I'd photocopy resources where to check and readings of the POWER SUPPLY being used on CATALYST and add on the

list of reference at the Hardware Control Room. For our reference. (Thank you Nasir for the manual).

- Run vhfst checkers, and encountered an error while running on the checkers.

- For more information, kindly checked the datalog failures at the directory /home/operator

-fail_powermi_033004

-vhf_dig_fail033004

- Reset the VHFDIG MF board - PACS1 (slot 5), still failing.

- Undocked the testhead and reset the VHFDIG CC (slot 11), still failing.

- Checked with Yeow for any spare board. Yeow checked 1 of the instrument being used and found that 1 fuse was busted, got

1 fuse at T05-CAT. run vhfst checkers, passed. (This instrument is called as DOWN CONVERTER).

- Redo the set-up but failing OPEN_FAIL on 2 pins, pin192 and pin162.

Solution:

- Tried undocking and re-docking but still encountered the same failure.

- Run continuity_mi checkers to check any failure on these 2pins - no failure found.

- Redo again the set-up, luckily it was up at 1540hrs.

- Managed to finish 2 wafers at B-shift.

1st PIN - 8 um

Conti Pass - 18um

Overdrive - 42 um

Effective Overdrive - 22um

Conclusion:

SWPS1 Slot 5 5.2V not accurate & DOWN CONVERTER fuse busted.

Remarks:

N/A.

Done by: Edmar Estrada Espiritu (Wafer Sort Team, Line Engineer).